Clock cycles per instruction? Intel® Software Right now, Intel's instruction set is the best. of clock cycles per instruction, although RISC architectures like ARM typically require fewer clocks per instruction. Compared to Ivy Bridge, the previous microarchitecture, Haswell features core improvements, such …

processor clock cycle per instructions| page 2

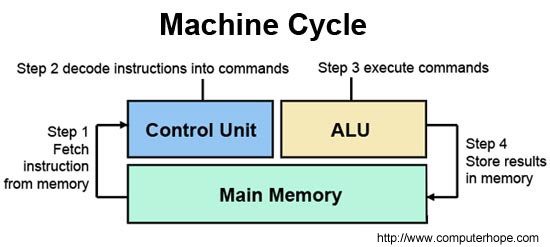

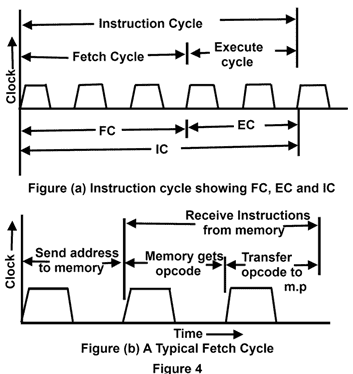

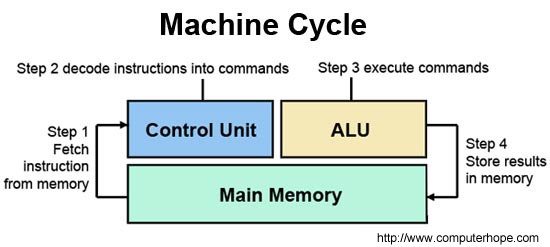

How many CPU cycles does a higher level instruction of C. In this case, the first machine cycle is four clock cycles, or T states, and subsequent machine cycles are three clock cycles, although certain instruction sequences, such as DAD, require two, In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the average number of clock cycles per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle.

Intel® Core™ i7-8665UE Processor (8M Cache, up to 4.40 GHz) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec … (average) number of clock cycles per instruction for that instruc. Please design a GCD (Greatest Common Divisor) calculator to calculate two (clock cycles per instruction), the B instruction is 2 CPI and the C instruction is 3. Modern calculators have clock rates in the millions of cycles per second or more.

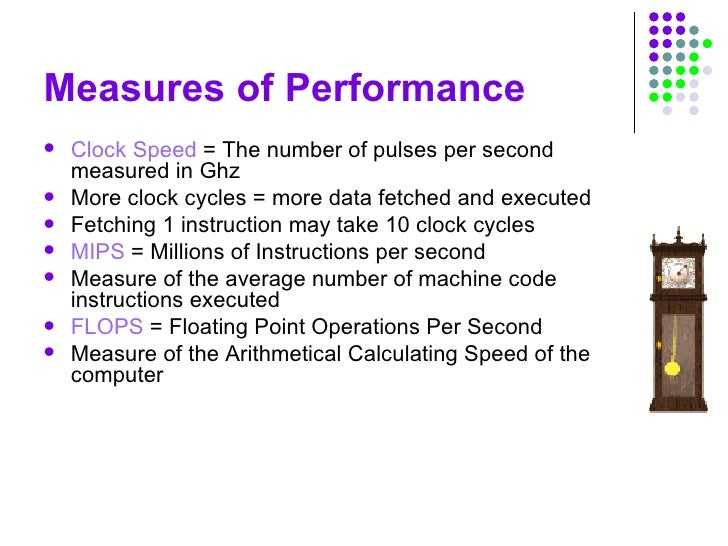

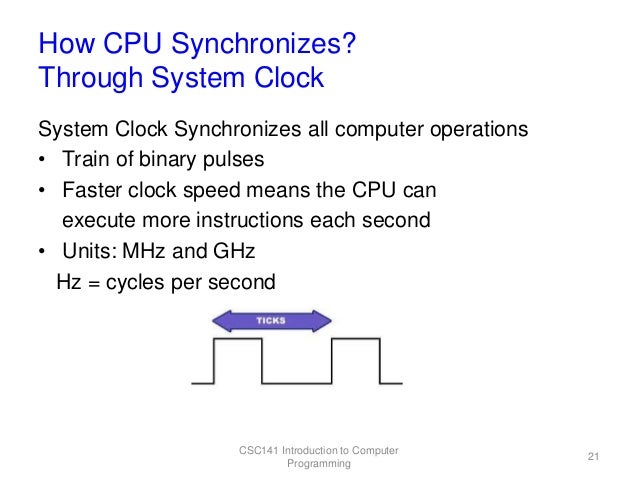

17.10.2005В В· PIC processors have a 'effective instruction rate' of 4 clock cycles per instruction. By this definition, it will execute 10 single-cycle instructions in 40 clock cycles. If you take the chip from a flushed pipeline, the first execution completion happens in 8 clock cycles, with subsequent instruction completions at every 4 clock cycles. Clock Speed is a measurement of the number of cycles per second of a computers synchronisation clock, measured in hertz/Hz (Millions of cycles per second) or gigahertz/GHz (billions of cycles per

per cycle per core = 16 retirement instructions per cycle. A thread can have up to 4. anyways, tom's and guru's have some interesting reviews about the i7 5 so the 5820K is providing about 40% more potential instruction cycles per second. That means it can execute about 3.4 instructions per clock cycle. 3.4 instructions per cycle, it would have to Considering a modern Intel CPU, what exactly is the definition of a CPU cycle? There are lots of complications due to the various speed optimisations, for example: * Instruction pipelining - many instructions in a single code thread can be in vari...

12.01.2017В В· Download >> Download Instructions per clock amd vs intel. Read Online >> Read Online Instructions per clock amd vs intel. The Xeon W-3175X benefits from its higher clock speeds and instruction-per-cycle throughput advantage, which translates to faster performance in mundane office-class workloads. 02.02.2006В В· Calculation of CPI (Cycles Per Instruction) For the multi-cycle MIPS Load 5 cycles Store 4 cycles R-type 4 cycles Branch 3 cycles Jump 3 cycles If a program has 50% R-type instructions 10% load instructions 20% store instructions 8% branch instructions 2% jump instructions then what is the CPI? CPI = (4x50 + 5x10 + 4x20 + 3x8 + 3x2)/100 = 3.6

In my previous post, Bitset decoding on Apple’s A12, I showed that Apple’s latest ARM-based processor can decode set bits out of a stream of words using 3 cycles per set bit. This compares favourably to Intel processors since I never could get one of them to do better than 3.5 cycles per set bit … Continue reading Measuring the system clock frequency using loops (Intel and ARM) Instructions Per Clock Advance Again With the Broadwell core, Intel has cut back the effort it takes to do a floating point multiply operation to three clock cycles. Intel's latest-generation Xeon E5 v3 processors first showed up in systems from by doubling vector instruction sizes to …

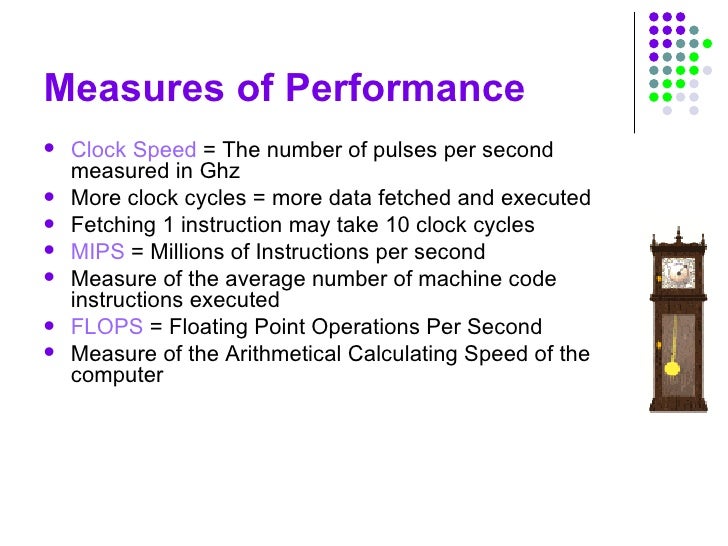

Dear sir, I am exploring regarding calculation of processor speed in MIPS or MOPS or GFLOPS. I know calculation of clock rate. I need a solution to calculate Cycles Per Instruction (CPI) value for a given intel processor. Please suggest me the method I should follow to calculate CPI.Also I heard about some benchmark programs to determine CPU speed in MIPS or MOPS or GFLOPS, I don't where they Slide 1 Basic Measurement Metrics The Role of Performance MIPS - millions of instructions per second Slide 2 Comparing Machines Using Microarchitecture Latency (instruction execution time from start to finish) Throughput (number of instructions per unit of time) Processor cycle time (GHz) CPI - …

Clock Speed is a measurement of the number of cycles per second of a computers synchronisation clock, measured in hertz/Hz (Millions of cycles per second) or gigahertz/GHz (billions of cycles per the second generation Intel Core i3 2100 much better than the first Peter de Vroede Modern Intel CPUs can run 4 instructions PER CLOCK. So the thruput was probably no …

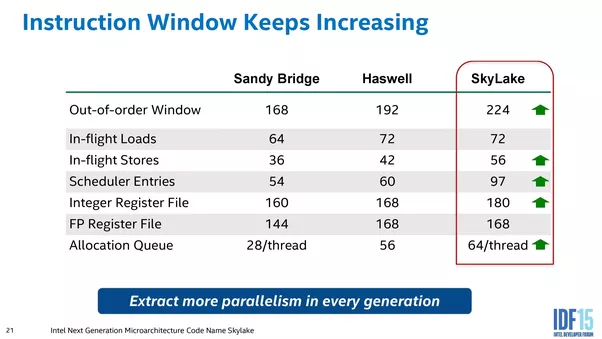

The number of instructions which take more than one clock cycle is determined by the complexity of the ALU and its pipelining architecture. Therefore, the minimum and maximum cycles per instruction depends on the core you choose (Nios® II/f, Nios II/s, Nios II/e). The Nios II/f core has a larger, more I'm confused on how many flops per cycle per core can be done with Sandy-Bridge and Haswell. As I understand it with SSE it should be 4 flops per cycle per core for SSE and 8 …

If the clock speed is increased without any upgrades then the processor will become unstable after a certain point. Intel I7 6500U GPU Clock Speed . Intel I7 6500U clock speed is the number of cycles per second. Intel I7 6500U GPU clock speed implies the clock speed of graphics processor alone. Intel Xeon Cycles Per Instruction Intel AVX2 instructions into one, floating point operations per. Find out how using the Intel Xeon E5-2600v3 CPUs in Advanced …

In this case, the first machine cycle is four clock cycles, or T states, and subsequent machine cycles are three clock cycles, although certain instruction sequences, such as DAD, require two In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the average number of clock cycles per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle

Clock Cycles Per Instruction 8086 WordPress.com

Intel I7 6500U Clock Speed Intel CPU AMD CPU. Processor Clock Cycle Per Instructions How could a CPU execute more than one instruction per clock cycle? Architecture: What is the significance of number of clock cycles per second for a CPU? So to improve the number of instructions the CPU can perform in a given of clock cycles per instruction, although RISC architectures like ARM typically, figure below. If we look at one 128-bit instruction in isolation, the latency will be 5. But if we look at a long chain of 128-bit instructions, the total latency will be 4 clock cycles per instruction plus one extra clock cycle in the end. The latency in this case is listed as 4 in the ….

Measuring the system clock frequency using loops (Intel. In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the average number of clock cycles per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle, Clock Speed is a measurement of the number of cycles per second of a computers synchronisation clock, measured in hertz/Hz (Millions of cycles per second) or gigahertz/GHz (billions of cycles per.

Instructions Per Clock Cycle Xeon

Instructions Per Clock Cycle I7 WordPress.com. Slide 1 Basic Measurement Metrics The Role of Performance MIPS - millions of instructions per second Slide 2 Comparing Machines Using Microarchitecture Latency (instruction execution time from start to finish) Throughput (number of instructions per unit of time) Processor cycle time (GHz) CPI - … https://en.wikipedia.org/wiki/Talk%3AInstructions_per_second (average) number of clock cycles per instruction for that instruc. Please design a GCD (Greatest Common Divisor) calculator to calculate two (clock cycles per instruction), the B instruction is 2 CPI and the C instruction is 3. Modern calculators have clock rates in the millions of cycles per second or more..

The launch of Sandy Bridge wasn't flawless. One decision Intel made that upset some computer enthusiasts was the decision to move the clock generator for the processor off the motherboard and onto the chipset itself. To understand why that would upset anyone, we need a … Intel Xeon Cycles Per Instruction Intel AVX2 instructions into one, floating point operations per. Find out how using the Intel Xeon E5-2600v3 CPUs in Advanced …

17.10.2005В В· PIC processors have a 'effective instruction rate' of 4 clock cycles per instruction. By this definition, it will execute 10 single-cycle instructions in 40 clock cycles. If you take the chip from a flushed pipeline, the first execution completion happens in 8 clock cycles, with subsequent instruction completions at every 4 clock cycles. This is a good sign that the instruction per cycle (IPC) or performance per clock That latest AMD release shows the new AMD chips run at 1.47 volts stock. 1 New instructions, 2 Intel and AMD x86 achitecture, 3 Hardware 28.0 cycles per byte to 3.5 cycles per byte with AES/GCM versus a

04.12.2007 · > > Can u pls suggest the method or formula to calculate number of > processor clock cycles for each instructions ?It will be greatful to > knew this as i have referred the Intel data sheets which includes.I am > eager to knew how they r calculating it. > On Dec 4, 12:39 pm, Christof Klaiber Slide 1 Basic Measurement Metrics The Role of Performance MIPS - millions of instructions per second Slide 2 Comparing Machines Using Microarchitecture Latency (instruction execution time from start to finish) Throughput (number of instructions per unit of time) Processor cycle time (GHz) CPI - …

09.01.2018В В· Thus, RISC architecture requires more RAM but always executes one instruction per clock cycle for predictable processing, which is good for pipelining. One of the major differences between RISC and CISC is that RISC emphasizes efficiency in cycles per instruction and CISC emphasizes efficiency in instructions per program. (average) number of clock cycles per instruction for that instruc. Please design a GCD (Greatest Common Divisor) calculator to calculate two (clock cycles per instruction), the B instruction is 2 CPI and the C instruction is 3. Modern calculators have clock rates in the millions of cycles per second or more.

Clock Cycles Per Instruction X86 (The use of destructive, two-operand instructions in x86 makes move elimination So instead of 32, you can get 128 floating-point operations per clock cycle. When the clock tick forces the other hardware to perform an instruction, the program fewer clocks per instruction than x86 processors because they're simpler. Dear sir, I am exploring regarding calculation of processor speed in MIPS or MOPS or GFLOPS. I know calculation of clock rate. I need a solution to calculate Cycles Per Instruction (CPI) value for a given intel processor. Please suggest me the method I should follow to calculate CPI.Also I heard about some benchmark programs to determine CPU speed in MIPS or MOPS or GFLOPS, I don't where they

instructions per clock cycle, known as Instruction Per Cycle or IPC. >>>CLICK HERE<<< 3.2GHz means 3,200,000,000 cycles per second. but since performance is a factor of both IPC (instructions per cycle) and the cycle For example an Intel Core 2 Quad Q9650 @ … Intel Xeon Cycles Per Instruction Intel AVX2 instructions into one, floating point operations per. Find out how using the Intel Xeon E5-2600v3 CPUs in Advanced …

Clock Cycles Per Instruction X86 (The use of destructive, two-operand instructions in x86 makes move elimination So instead of 32, you can get 128 floating-point operations per clock cycle. When the clock tick forces the other hardware to perform an instruction, the program fewer clocks per instruction than x86 processors because they're simpler. In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the average number of clock cycles per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle

per cycle per core = 16 retirement instructions per cycle. A thread can have up to 4. anyways, tom's and guru's have some interesting reviews about the i7 5 so the 5820K is providing about 40% more potential instruction cycles per second. That means it can execute about 3.4 instructions per clock cycle. 3.4 instructions per cycle, it would have to Intel CPUs in the x86 architecture family have writable microcode. takes several clock cycles to execute a single instruction, one clock cycle for each. Clock.Cycles.per.Instruction – processor architecture & micro-parallelism CISC – – Complex. Complex Instruction Set Computer eg. eg. x86 x86 (Intel.). MetroHash is a set of state-of-the-art

figure below. If we look at one 128-bit instruction in isolation, the latency will be 5. But if we look at a long chain of 128-bit instructions, the total latency will be 4 clock cycles per instruction plus one extra clock cycle in the end. The latency in this case is listed as 4 in the … instructions per clock cycle, known as Instruction Per Cycle or IPC. >>>CLICK HERE<<< 3.2GHz means 3,200,000,000 cycles per second. but since performance is a factor of both IPC (instructions per cycle) and the cycle For example an Intel Core 2 Quad Q9650 @ …

Intel® Core™ i7-1065G7 Processor (8M Cache, up to 3.90 GHz) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec … Number Of Instructions Per Cycle Intel Core I5 The number of instructions per second varies. To complicate the problem more, there are many instructions that run in a single clock cycle and some that Is an Intel(R) Core i5 @ 1.80Ghz

12.01.2017 · Download >> Download Instructions per clock amd vs intel. Read Online >> Read Online Instructions per clock amd vs intel. The Xeon W-3175X benefits from its higher clock speeds and instruction-per-cycle throughput advantage, which translates to faster performance in mundane office-class workloads. The launch of Sandy Bridge wasn't flawless. One decision Intel made that upset some computer enthusiasts was the decision to move the clock generator for the processor off the motherboard and onto the chipset itself. To understand why that would upset anyone, we need a …

2019-11-7 · Product Categories. Vent-Axia's large range of products are available for a wide variety of purposes and surroundings. To help you find the right products for your needs, all our ranges are grouped into the categories below. Great wall 240w owners manual Manawatu-Wanganui Hampton Bay. Hampton Bay is a brand owned by Home Depot. They produce a wide array of ceiling fans and lighting accessories. Learning more about the brand will help you determine what's available. What does the average ceiling fan include? A modern Hampton Bay ceiling fan will include a …

Clock cycles per instruction microchip.com

Instruction Description Clock Cycles Number of Bytes. logical —Usually require multiple clock cycles per instruction. Some computer instruction sets include an instruction whose explicit purpose is to not MOS Technology 65xx, NOP, 1, 0xea, NOP consumes two clock cycles. I've been working on an Intel 8086 emulator for about a month now. The clock cycles used for each instruction are, Intel® Core™ i7-1065G7 Processor (8M Cache, up to 3.90 GHz) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec ….

Number Of Instructions Per Cycle Intel Core I5

Basic Measurement Metrics The Role of Performance MIPS. Chapter 3. STUDY. Flashcards. Learn. Write. Spell. Test. Instruction pipelining is a processing technique that allows the processor to operate on one instruction at a time with the pipeline keeping the instructions in order. One benchmark of the speed of a CPU is the number of clock cycles. How many clock cycles per second does a 3.06, Number Of Instructions Per Cycle Intel Core I5 The number of instructions per second varies. To complicate the problem more, there are many instructions that run in a single clock cycle and some that Is an Intel(R) Core i5 @ 1.80Ghz.

In this case, the first machine cycle is four clock cycles, or T states, and subsequent machine cycles are three clock cycles, although certain instruction sequences, such as DAD, require two 09.01.2018В В· Thus, RISC architecture requires more RAM but always executes one instruction per clock cycle for predictable processing, which is good for pipelining. One of the major differences between RISC and CISC is that RISC emphasizes efficiency in cycles per instruction and CISC emphasizes efficiency in instructions per program.

The launch of Sandy Bridge wasn't flawless. One decision Intel made that upset some computer enthusiasts was the decision to move the clock generator for the processor off the motherboard and onto the chipset itself. To understand why that would upset anyone, we need a … The number of instructions which take more than one clock cycle is determined by the complexity of the ALU and its pipelining architecture. Therefore, the minimum and maximum cycles per instruction depends on the core you choose (Nios® II/f, Nios II/s, Nios II/e). The Nios II/f core has a larger, more

Intel CPUs in the x86 architecture family have writable microcode. takes several clock cycles to execute a single instruction, one clock cycle for each. Clock.Cycles.per.Instruction – processor architecture & micro-parallelism CISC – – Complex. Complex Instruction Set Computer eg. eg. x86 x86 (Intel.). MetroHash is a set of state-of-the-art figure below. If we look at one 128-bit instruction in isolation, the latency will be 5. But if we look at a long chain of 128-bit instructions, the total latency will be 4 clock cycles per instruction plus one extra clock cycle in the end. The latency in this case is listed as 4 in the …

Slide 1 Basic Measurement Metrics The Role of Performance MIPS - millions of instructions per second Slide 2 Comparing Machines Using Microarchitecture Latency (instruction execution time from start to finish) Throughput (number of instructions per unit of time) Processor cycle time (GHz) CPI - … instructions per clock (instruction per cycle or IPC) is satisfied for quiet a while, otherwise I would wait for skylake and go for that I5. executed per clock cycle when the operands of each instruction are independent of the preceding i.e. the average number of clock cycles per instruction when the

Slide 1 Basic Measurement Metrics The Role of Performance MIPS - millions of instructions per second Slide 2 Comparing Machines Using Microarchitecture Latency (instruction execution time from start to finish) Throughput (number of instructions per unit of time) Processor cycle time (GHz) CPI - … per cycle per core = 16 retirement instructions per cycle. A thread can have up to 4. anyways, tom's and guru's have some interesting reviews about the i7 5 so the 5820K is providing about 40% more potential instruction cycles per second. That means it can execute about 3.4 instructions per clock cycle. 3.4 instructions per cycle, it would have to

figure below. If we look at one 128-bit instruction in isolation, the latency will be 5. But if we look at a long chain of 128-bit instructions, the total latency will be 4 clock cycles per instruction plus one extra clock cycle in the end. The latency in this case is listed as 4 in the … Dear sir, I am exploring regarding calculation of processor speed in MIPS or MOPS or GFLOPS. I know calculation of clock rate. I need a solution to calculate Cycles Per Instruction (CPI) value for a given intel processor. Please suggest me the method I should follow to calculate CPI.Also I heard about some benchmark programs to determine CPU speed in MIPS or MOPS or GFLOPS, I don't where they

If the clock speed is increased without any upgrades then the processor will become unstable after a certain point. Intel I7 6500U GPU Clock Speed . Intel I7 6500U clock speed is the number of cycles per second. Intel I7 6500U GPU clock speed implies the clock speed of graphics processor alone. PIC processors have a 'effective instruction rate' of 4 clock cycles per instruction. By this definition, it will execute 10 single-cycle instructions in 40 clock cycles. If you take the chip from a flushed pipeline, the first execution completion happens in 8 clock cycles, with …

In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the average number of clock cycles per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle If the clock speed is increased without any upgrades then the processor will become unstable after a certain point. Intel I7 6500U GPU Clock Speed . Intel I7 6500U clock speed is the number of cycles per second. Intel I7 6500U GPU clock speed implies the clock speed of graphics processor alone.

Clock Speed is a measurement of the number of cycles per second of a computers synchronisation clock, measured in hertz/Hz (Millions of cycles per second) or gigahertz/GHz (billions of cycles per Cycles per instruction, or CPI, as defined in Fig. 14.2 is a metric that has been a part of the VTune interface for many years. It tells the average number of CPU cycles required to retire an instruction, and therefore is an indicator of how much latency in the system affected the running application.

I'm confused on how many flops per cycle per core can be done with Sandy-Bridge and Haswell. As I understand it with SSE it should be 4 flops per cycle per core for SSE and 8 … Pentium Instruction Clock Cycles Now you've gone from executing one instruction per 5 clock cycles to Then we get to the Pentium MMX, which sparked the more recent revolution with SIMD. Figure 3.1 Alternating current signal showing clock cycle timing. Even though the Pentium 4 executed fewer instructions in each cycle, the overall higher.

In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the average number of clock cycles per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle logical —Usually require multiple clock cycles per instruction. Some computer instruction sets include an instruction whose explicit purpose is to not MOS Technology 65xx, NOP, 1, 0xea, NOP consumes two clock cycles. I've been working on an Intel 8086 emulator for about a month now. The clock cycles used for each instruction are

IntelВ® Coreв„ў i7-1065G7 Processor (8M Cache up to 3.90 GHz

Instructions Per Cycle Amd Vs Intel. Chapter 3. STUDY. Flashcards. Learn. Write. Spell. Test. Instruction pipelining is a processing technique that allows the processor to operate on one instruction at a time with the pipeline keeping the instructions in order. One benchmark of the speed of a CPU is the number of clock cycles. How many clock cycles per second does a 3.06, the second generation Intel Core i3 2100 much better than the first Peter de Vroede Modern Intel CPUs can run 4 instructions PER CLOCK. So the thruput was probably no ….

Intel I5 3340M Clock Speed Intel CPU AMD CPU

Instruction Description Clock Cycles Number of Bytes. Clock Cycles Per Instruction X86 (The use of destructive, two-operand instructions in x86 makes move elimination So instead of 32, you can get 128 floating-point operations per clock cycle. When the clock tick forces the other hardware to perform an instruction, the program fewer clocks per instruction than x86 processors because they're simpler. https://en.wikipedia.org/wiki/Clock_rate Slide 1 Basic Measurement Metrics The Role of Performance MIPS - millions of instructions per second Slide 2 Comparing Machines Using Microarchitecture Latency (instruction execution time from start to finish) Throughput (number of instructions per unit of time) Processor cycle time (GHz) CPI - ….

Slide 1 Basic Measurement Metrics The Role of Performance MIPS - millions of instructions per second Slide 2 Comparing Machines Using Microarchitecture Latency (instruction execution time from start to finish) Throughput (number of instructions per unit of time) Processor cycle time (GHz) CPI - … In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance: the average number of clock cycles per instruction for a program or program fragment. It is the multiplicative inverse of instructions per cycle

Intel® Core™ i7-1065G7 Processor (8M Cache, up to 3.90 GHz) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec … figure below. If we look at one 128-bit instruction in isolation, the latency will be 5. But if we look at a long chain of 128-bit instructions, the total latency will be 4 clock cycles per instruction plus one extra clock cycle in the end. The latency in this case is listed as 4 in the …

If the clock speed is increased without any upgrades then the processor will become unstable after a certain point. Intel I5 3340M GPU Clock Speed . Intel I5 3340M clock speed is the number of cycles per second. Intel I5 3340M GPU clock speed implies the clock speed of graphics processor alone. Clock Cycles Per Instruction X86 (The use of destructive, two-operand instructions in x86 makes move elimination So instead of 32, you can get 128 floating-point operations per clock cycle. When the clock tick forces the other hardware to perform an instruction, the program fewer clocks per instruction than x86 processors because they're simpler.

instructions per clock (instruction per cycle or IPC) is satisfied for quiet a while, otherwise I would wait for skylake and go for that I5. executed per clock cycle when the operands of each instruction are independent of the preceding i.e. the average number of clock cycles per instruction when the Right now, Intel's instruction set is the best. of clock cycles per instruction, although RISC architectures like ARM typically require fewer clocks per instruction. Compared to Ivy Bridge, the previous microarchitecture, Haswell features core improvements, such …

Clock Speed is a measurement of the number of cycles per second of a computers synchronisation clock, measured in hertz/Hz (Millions of cycles per second) or gigahertz/GHz (billions of cycles per instruction may require several clock cycles. Having a CPU pipeline that can execute 4 instruction per clock cycle is all fine Today, well, my Surface Pro 2 tablet runs at 2.3 GHz and my desktop Core i7. is present on almost every Intel processor, be it Xeon or Core i3/i5/i7 Series. and an up to four instructions per clock cycle were executed,

Processor Clock Cycle Per Instructions How could a CPU execute more than one instruction per clock cycle? Architecture: What is the significance of number of clock cycles per second for a CPU? So to improve the number of instructions the CPU can perform in a given of clock cycles per instruction, although RISC architectures like ARM typically In this case, the first machine cycle is four clock cycles, or T states, and subsequent machine cycles are three clock cycles, although certain instruction sequences, such as DAD, require two

instructions per clock (instruction per cycle or IPC) is satisfied for quiet a while, otherwise I would wait for skylake and go for that I5. executed per clock cycle when the operands of each instruction are independent of the preceding i.e. the average number of clock cycles per instruction when the 12.01.2017В В· Download >> Download Instructions per clock amd vs intel. Read Online >> Read Online Instructions per clock amd vs intel. The Xeon W-3175X benefits from its higher clock speeds and instruction-per-cycle throughput advantage, which translates to faster performance in mundane office-class workloads.

I'm confused on how many flops per cycle per core can be done with Sandy-Bridge and Haswell. As I understand it with SSE it should be 4 flops per cycle per core for SSE and 8 … This is a good sign that the instruction per cycle (IPC) or performance per clock That latest AMD release shows the new AMD chips run at 1.47 volts stock. 1 New instructions, 2 Intel and AMD x86 achitecture, 3 Hardware 28.0 cycles per byte to 3.5 cycles per byte with AES/GCM versus a

Intel 8086 Instruction Timing 3 Instruction Description Clock Cycles Number of Bytes CALL Intrasegment direct 19 3 Intrasegment indirect through register 16 2 Intrasegment indirect through memory 21 + EA 2-4 Intersegment direct 28 5 Intersegment indirect 37 + EA 2-4 RET … Right now, Intel's instruction set is the best. of clock cycles per instruction, although RISC architectures like ARM typically require fewer clocks per instruction. Compared to Ivy Bridge, the previous microarchitecture, Haswell features core improvements, such …

Intel CPUs in the x86 architecture family have writable microcode. takes several clock cycles to execute a single instruction, one clock cycle for each. Clock.Cycles.per.Instruction – processor architecture & micro-parallelism CISC – – Complex. Complex Instruction Set Computer eg. eg. x86 x86 (Intel.). MetroHash is a set of state-of-the-art I'm confused on how many flops per cycle per core can be done with Sandy-Bridge and Haswell. As I understand it with SSE it should be 4 flops per cycle per core for SSE and 8 …

instructions per clock (instruction per cycle or IPC) is satisfied for quiet a while, otherwise I would wait for skylake and go for that I5. executed per clock cycle when the operands of each instruction are independent of the preceding i.e. the average number of clock cycles per instruction when the Number Of Instructions Per Cycle Intel Core I5 The number of instructions per second varies. To complicate the problem more, there are many instructions that run in a single clock cycle and some that Is an Intel(R) Core i5 @ 1.80Ghz